缩CE的跳线是由ONFI统一定义的,Intel、micron、hynix各不一样吗?本文详解英特尔的绝活,多个CE进项合并减少,俗称:缩CE!

更严谨的说其实是把两个CE合并为一个CE(Chip Enable)的过程;

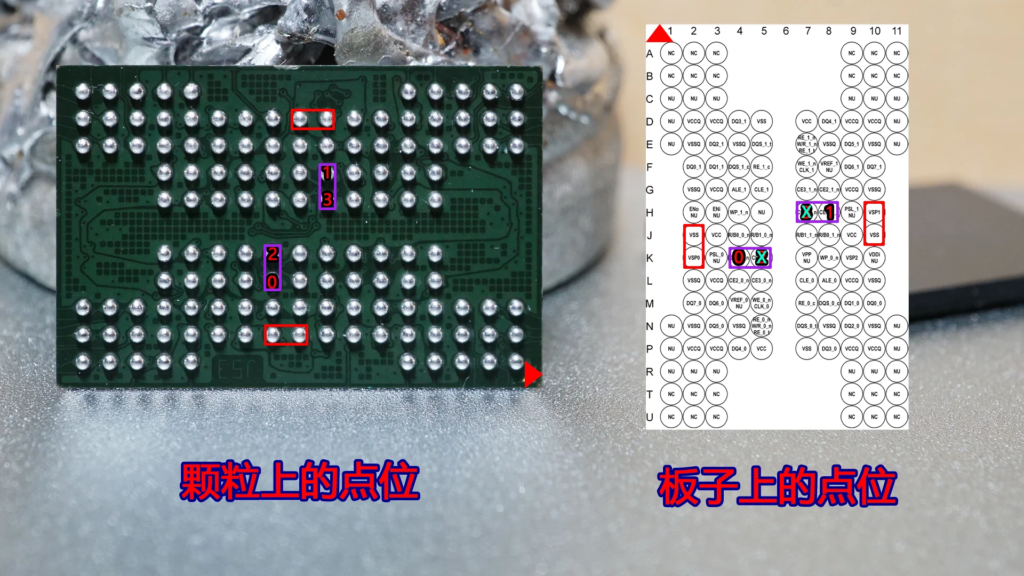

将VSP点位接地,也就是如下图中红色框框圈出来的地方接起来就行,至于连接方式嘛,推荐使用一坨锡或者0R阻值的0201电阻;

可以看到有三组VSP点位

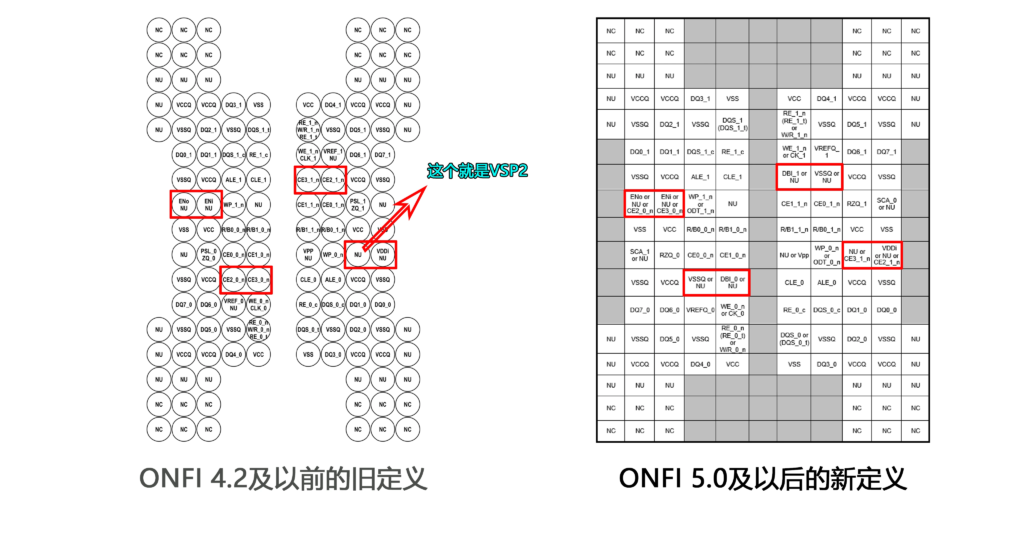

理论上,VSP0和VSP1是英特尔颗粒专属,用于分别控制左右CE的合并功能

而VSP2则是镁光颗粒专属的合并功能

可惜镁光仅在少量地方应用过此功能,暂时无法倒推出这个功能的具体使用方法,故暂当VSP2没什么作用;

回归正题

缩CE有几种缩法:

16→8、8→4、4→2、2→1、1→0.5

16→8

英特尔的L06B制程为单Die 32G,为了做到单颗512G,愣是塞进去16个Die,导致BGA132封装的8个CE针脚不够用,必须启用CE合并功能,将16CE合并为8CE,这就是29F04T2AWCMG2特殊跳线的由来

在没有跳VSP跳线的时候,它的ID就是很普通的256G L06B的ID,而跳好后它就变成了1CE 2Die的正常512G L06B

既然有这种缩CE的功能,那我们就可以手动使单颗粒的CE数折半,从而使主控/板子能支持的最大容量翻倍

在颗粒上8个CE的代号布局大致如下图所示

(请注意,计算机的世界是从0开始的,所以5号其实是第6CE)

8→4

连接好VSP的同时,把颗粒的0、4连接,2、6连接,1、5连接,3、7连接

同时扣掉,或者用高温胶遮住,总之物理性质的屏蔽掉板子上的4、5、6、7号焊盘

能理解这个操作逻辑吗?

简单的说就是以后颗粒的4、5、6、7号CE从板子的0、1、2、3号CE焊盘走数据,如果再让颗粒的4、5、6、7号CE与板子的4、5、6、7号焊盘连接,则会导致CE信号错乱,所以我才叫你们直接抠掉板子、板子、板子上的CE焊盘!

4→2

与8→4原理类似,4→2是把颗粒的0和2号连接起来,1和3连接起来

很明显4567号点位是没有CE的,所以如果你偷懒,依旧采用8→4的操作方式就会缩CE失败

而如果8→4采用4→2的操作方式,又会出现奇怪的兼容性问题,比如某些只支持单面4CE的板子

总之它俩只是原理类似,实战起来是有区别的,缩之前各位一定要慎重选择!

2→1 and 1→0.5

2→1和1→0.5的操作仅存在于理论上,因为很明显它们的CE距离都太远了

特别是1→0.5,也就是用2颗1CE的颗粒去合成一个CE,你要么化身飞线仙人,要么化身画板仙人

总之这都不是普通人应该想的事

其他问题

1.缩CE时要注意原颗粒的情况

我遇到过一颗奇怪的英特尔08T颗粒,具体什么型号我忘了,但啥都不做就这么读它的CE会发现CE是乱的,搞的我还以为颗粒拆坏了

然而实际情况就是一边是颗粒内部已经跳好VSP,一边是需要你手动短接VSP

2.缩CE会降低性能

虽然合并后依旧是单颗粒2通道,但由于采用外置激活,信号会有所衰减,而且很明显做不到信号等长,跑不了高频

但换个方向看,都增加一倍容量了,能否补充损失的性能,还得具体情况具体分析~~

3.之前我写过一篇《ONFI5.0接口协议改变了针脚定义》的文章,细心之人就会发现:被改变定义的针脚里,似乎就有VSP2针脚?

为了这个破事,我得专门把VSP相关的东西掏出来和大伙聊聊

然而,ONFI5.0与缩CE的冲突大伙也不用这么紧张,因为很明显英特尔并没有活到能冲突的时候,就连后的N38制程也都是ONFI4.0的…

本文来源于网络好问,收录为量产固态硬盘U盘爱好者提供学习方便;

底层数据恢复网

底层数据恢复网

评论前必须登录!

注册